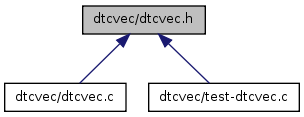

This graph shows which files directly or indirectly include this file:

Classes | |

| struct | dtcvec_reginfo |

Defines | |

| #define | MRA_SZm 0x01 |

| #define | MRA_SZ_BYTE 0x00 |

| #define | MRA_SZ_WORD 0x01 |

| #define | MRA_DTSm 0x02 |

| #define | MRA_DTS_DA 0x00 |

| #define | MRA_DTS_SA 0x02 |

| #define | MRA_MDm 0x04 |

| #define | MRA_MD0m 0x04 |

| #define | MRA_MD1m 0x08 |

| #define | MRA_MD_NORMAL 0x00 |

| #define | MRA_MD_REPEAT 0x04 |

| #define | MRA_MD_BLOCK 0x08 |

| #define | MRA_DMm 0x30 |

| #define | MRA_DM0m 0x10 |

| #define | MRA_DM1m 0x20 |

| #define | MRA_DM_FIXED 0x00 |

| #define | MRA_DM_INC 0x20 |

| #define | MRA_DM_DEC 0x10 |

| #define | MRA_SMm 0xc0 |

| #define | MRA_SM0m 0x40 |

| #define | MRA_SM1m 0x80 |

| #define | MRA_SM_FIXED 0x00 |

| #define | MRA_SM_INC 0x80 |

| #define | MRA_SM_DEC 0x40 |

| #define | MRB_DISELm 0x40 |

| #define | MRB_CHNEm 0x80 |

| #define | DTCVEC_RIS __PORT32 0xFFEBC0 |

| #define | DTCVEC_RIE __PORT32 0xFFEFBF |

| #define | DTCVEC __PORT16 0x000400 |

| #define | DTCVEC_SW 0 |

| #define | DTCVEC_IRQ0 16 |

| #define | DTCVEC_IRQ1 17 |

| #define | DTCVEC_IRQ2 18 |

| #define | DTCVEC_IRQ3 19 |

| #define | DTCVEC_IRQ4 20 |

| #define | DTCVEC_IRQ5 21 |

| #define | DTCVEC_ADI 28 |

| #define | DTCVEC_TGI0A 32 |

| #define | DTCVEC_TGI0B 33 |

| #define | DTCVEC_TGI0C 34 |

| #define | DTCVEC_TGI0D 35 |

| #define | DTCVEC_TGI1A 40 |

| #define | DTCVEC_TGI1B 41 |

| #define | DTCVEC_TGI2A 44 |

| #define | DTCVEC_TGI2B 45 |

| #define | DTCVEC_TGI3A 48 |

| #define | DTCVEC_TGI3B 49 |

| #define | DTCVEC_TGI3C 50 |

| #define | DTCVEC_TGI3D 51 |

| #define | DTCVEC_TGI4A 56 |

| #define | DTCVEC_TGI4B 57 |

| #define | DTCVEC_TGI5A 60 |

| #define | DTCVEC_TGI5B 61 |

| #define | DTCVEC_RXI0 81 |

| #define | DTCVEC_TXI0 82 |

| #define | DTCVEC_RXI1 85 |

| #define | DTCVEC_TXI1 86 |

| #define | DTCVEC_RXI2 89 |

| #define | DTCVEC_TXI2 90 |

| #define | DTCVEC_IICI0 100 |

| #define | DTCVEC_IICI1 102 |

| #define | DTCVEC_CMI1 104 |

| #define | DTCVEC_CMI2 105 |

| #define | DTCVEC_HCAN1 107 |

| #define | DTCVEC_HCAN0 109 |

Functions | |

| void * | dtcvec_alloc (size_t size) |

| DTC - DATA TRANSFER CONTROLLER. | |

| void * | dtcvec_get (int vectnum) |

| Get address of the register information from the vector table. | |

| void * | dtcvec_set (int vectnum, void *vect) |

| Assign the DTC vector address to appropriate register information. | |

| void | dtcvec_print () |

| void | dtcvec_fillreg (void *vect, struct dtcvec_reginfo *reginfo) |

| Fill the register memory with the prepared data structure of register information (align bytes correctly in the memory). | |

Define Documentation

| #define DTCVEC __PORT16 0x000400 |

| #define DTCVEC_ADI 28 |

| #define DTCVEC_CMI1 104 |

| #define DTCVEC_CMI2 105 |

| #define DTCVEC_HCAN0 109 |

| #define DTCVEC_HCAN1 107 |

| #define DTCVEC_IICI0 100 |

| #define DTCVEC_IICI1 102 |

| #define DTCVEC_IRQ0 16 |

| #define DTCVEC_IRQ1 17 |

| #define DTCVEC_IRQ2 18 |

| #define DTCVEC_IRQ3 19 |

| #define DTCVEC_IRQ4 20 |

| #define DTCVEC_IRQ5 21 |

| #define DTCVEC_RIE __PORT32 0xFFEFBF |

| #define DTCVEC_RIS __PORT32 0xFFEBC0 |

| #define DTCVEC_RXI0 81 |

| #define DTCVEC_RXI1 85 |

| #define DTCVEC_RXI2 89 |

| #define DTCVEC_SW 0 |

| #define DTCVEC_TGI0A 32 |

| #define DTCVEC_TGI0B 33 |

| #define DTCVEC_TGI0C 34 |

| #define DTCVEC_TGI0D 35 |

| #define DTCVEC_TGI1A 40 |

| #define DTCVEC_TGI1B 41 |

| #define DTCVEC_TGI2A 44 |

| #define DTCVEC_TGI2B 45 |

| #define DTCVEC_TGI3A 48 |

| #define DTCVEC_TGI3B 49 |

| #define DTCVEC_TGI3C 50 |

| #define DTCVEC_TGI3D 51 |

| #define DTCVEC_TGI4A 56 |

| #define DTCVEC_TGI4B 57 |

| #define DTCVEC_TGI5A 60 |

| #define DTCVEC_TGI5B 61 |

| #define DTCVEC_TXI0 82 |

| #define DTCVEC_TXI1 86 |

| #define DTCVEC_TXI2 90 |

| #define MRA_DM0m 0x10 |

| #define MRA_DM1m 0x20 |

| #define MRA_DM_DEC 0x10 |

| #define MRA_DM_FIXED 0x00 |

| #define MRA_DM_INC 0x20 |

| #define MRA_DMm 0x30 |

| #define MRA_DTS_DA 0x00 |

| #define MRA_DTS_SA 0x02 |

| #define MRA_DTSm 0x02 |

| #define MRA_MD0m 0x04 |

| #define MRA_MD1m 0x08 |

| #define MRA_MD_BLOCK 0x08 |

| #define MRA_MD_NORMAL 0x00 |

| #define MRA_MD_REPEAT 0x04 |

| #define MRA_MDm 0x04 |

| #define MRA_SM0m 0x40 |

| #define MRA_SM1m 0x80 |

| #define MRA_SM_DEC 0x40 |

| #define MRA_SM_FIXED 0x00 |

| #define MRA_SM_INC 0x80 |

| #define MRA_SMm 0xc0 |

| #define MRA_SZ_BYTE 0x00 |

| #define MRA_SZ_WORD 0x01 |

| #define MRA_SZm 0x01 |

| #define MRB_CHNEm 0x80 |

| #define MRB_DISELm 0x40 |

Function Documentation

| void* dtcvec_alloc | ( | size_t | size | ) |

DTC - DATA TRANSFER CONTROLLER.

DTC manipulation with the vector table. Allocate memory for the register information. Its not necessary, but may be a good idea to do so.

- Parameters:

-

size number of blocks (each 12Bytes)

- Returns:

- pointer to register information

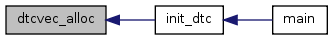

Here is the caller graph for this function:

| void dtcvec_fillreg | ( | void * | vect, | |

| struct dtcvec_reginfo * | reginfo | |||

| ) |

Fill the register memory with the prepared data structure of register information (align bytes correctly in the memory).

- Parameters:

-

*vect pointer to register information memory. *reginfo data structure of register information.

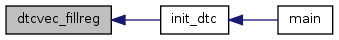

Here is the caller graph for this function:

| void* dtcvec_get | ( | int | vectnum | ) |

Get address of the register information from the vector table.

- Parameters:

-

vectnum vector number

- Returns:

- pointer to register information

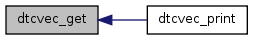

Here is the caller graph for this function:

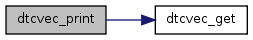

| void dtcvec_print | ( | ) |

Here is the call graph for this function:

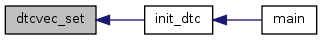

| void* dtcvec_set | ( | int | vectnum, | |

| void * | vect | |||

| ) |

Assign the DTC vector address to appropriate register information.

- Parameters:

-

vectnum vector number *vect pointer to register information

- Returns:

- the old vector

Here is the caller graph for this function:

1.7.1

1.7.1