TMS570LS3137: Difference between revisions

Hand made RPP SDRAM setup documentation to prepare for cleaning HalCoGen generated mess for HDK |

Fill in last HDK used setup (probably mess from HalCoGen). Requires checking. |

||

| Line 127: | Line 127: | ||

! SDTIMR !! !! !! | ! SDTIMR !! !! !! | ||

|- | |- | ||

| TRF_C (31-27) || | | TRF_C (31-27) || 5 || 9-1 || REFR to REFR | ||

|- | |- | ||

| T_RP (26-24) || | | T_RP (26-24) || 1 || 3-1 || PRE to ACTIV or REFR | ||

|- | |- | ||

| (23) || | | (23) || 0 || 0 || | ||

|- | |- | ||

| T_RCD (22-20) || | | T_RCD (22-20) || 1 || 3-1 || ACTIV to RD/WR | ||

|- | |- | ||

| (19) || | | (19) || 0 || 0 || | ||

|- | |- | ||

| T_WR (18-16) || | | T_WR (18-16) || 1 || 2-1 || WRITE to PRE | ||

|- | |- | ||

| T_RAS (15-12) || | | T_RAS (15-12) || 80 || 6-1 || ACTIV to PRE | ||

|- | |- | ||

| T_RC (11-8) || | | T_RC (11-8) || 5 || 9-1 || ACTIV to ACTIV | ||

|- | |- | ||

| (7) || | | (7) || 0 || 0 || | ||

|- | |- | ||

| T_RRD (6-4) || | | T_RRD (6-4) || 1 || 2-1 || ACTIV to ACTIV other bank | ||

|- | |- | ||

| (3) || | | (3) || 0 || 0 || | ||

|- | |- | ||

! SDSRETR !! !! !! | ! SDSRETR !! !! !! | ||

|- | |- | ||

| || | | || 0 || 5+3-1 || configure refresh rate | ||

|- | |- | ||

! SDRCR !! !! !! | ! SDRCR !! !! !! | ||

|- | |- | ||

| RR (12-0) || | | RR (12-0) || 2000 || 156 || 80e6 * 16e-3 / 8192 => less or equal to 156 | ||

|- | |- | ||

! SDCR !! !! !! | ! SDCR !! !! !! | ||

|- | |- | ||

| SR (31) || | | SR (31) || 0 || 0 || self refresh mode | ||

|- | |- | ||

| PD (30) || | | PD (30) || 0 || 0 || power down | ||

|- | |- | ||

| PDWR (29) || | | PDWR (29) || 0 || 0 || refresh in PD | ||

|- | |- | ||

| NM (14) || | | NM (14) || 1 || 1 || narrow mode | ||

|- | |- | ||

| CL (11-9) || | | CL (11-9) || 3 || 3 || CAS latency | ||

|- | |- | ||

| BIT11_9LOCK (8) || | | BIT11_9LOCK (8) || 1 || 1 || CAS latency lock | ||

|- | |- | ||

| IBANK (6-4) || | | IBANK (6-4) || 2 || 2 (4 banks) || banks | ||

|- | |- | ||

| PAGESIZE (2-0) || | | PAGESIZE (2-0) || 3 || 2 (10 bit) || counted in elements | ||

|} | |} | ||

===SCI port=== | ===SCI port=== | ||

Revision as of 22:13, 5 July 2014

Documentation

- Main TI page containing datasheets.

- TI TMS570 related forum

- TMS570 Wiki

- Media:Studim_procesoru.pdf Notes from documentation (in Czech language)

Programming

Tools recommended by TI for programming of this microcontroller:

- Code Composer Studio (runs on Win and Linux).

- HalCoGen (for Windows only, but also runs quite well in Wine).

CCS5.3.0.00090_linux in Ubuntu 12.04 64bits

After installation the application can be run with:

cd <install_dir>/ccsv5/eclipse/

./ccstudio

If the application fails to start is because CCS5 is a 32bits application a thus requires 32bits libraries:

sudo apt-get install libgtk2.0-0:i386 libxtst6:i386 gtk2-engines-pixbuf:i386 libcanberra-gtk-module:i386

If the application crashes with a segmentation fault do:

Edit <install_dir>/ccsv5/eclipse/plugins/com.ti.ccstudio.branding_<your version number>/plugin_customization.ini

And change key org.eclipse.ui/showIntro to false.

Choose "FREE License - for use with XDS100 JTAG Emulators" on the licensing options.

You may create a symbolic link and a desktop entry:

sudo ln -s <install_dir>/ccsv5/eclipse/ccstudio /usr/local/bin/ccstudio

And put in ~/.local/share/applications/ccs5.desktop

[Desktop Entry] Version=1.0 Type=Application Terminal=false Exec=ccstudio Name=Code Composer Studio Icon=/usr/local/ti/ccsv5/eclipse/icon.xpm

CCS5.5.0.00077_windows on Windows 7x64

Download ccs_setup_5.5.0.00077.exe from http://ti.com and run.

Choose component:

- Safety MCUs

Choose Compiler tools:

- TI ARM Compiler Tools

- TI Documentation

Coose JTAG Emulator Support

- XDS100 Class Emulator Support

FreeRTOS

Installation is easy, simply create new project in HalCoGen

- New -> Project

- Select Family:TMS570LS31x

- Select Device: TMS570LS3137ZWT_FREERTOS

All necessary files will be added into project automaticaly.

Matlab/Simulink Embedded Coder target

We have implemented support for Matlab/Simulink which allows to use designed peripherals support libraries from Simulink model design.

For further information look at separate pages for the target

http://rtime.felk.cvut.cz/rpp-tms570/

Hardware

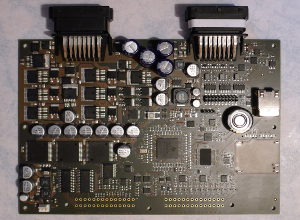

Developement board we are using: TMS570LS31x_HDK_Kit

SDRAM setup

- Simple code to setup SDRAM for use from OpenOCD and others code loaders

Setup of bit 31 in GPREG1 is required ele EMIF does not work as expected. From UM 4.3.3 Control of Special Multiplexed Options: Any application that requires the EMIF functionality must set GPREG1[31]. This allows these 8 EMIF module outputs to be driven on to the assigned balls.

systemREG1->GPREG1 |= 0x80000000;

| Parameter | Value for HDK | Value for RPP | Notice |

|---|---|---|---|

| Chip | IS45S16320 | ||

| banks | 4 (2 bits) | ||

| rows | 1024 (10 bits) | ||

| columns | 8192 (13 bits) | ||

| CL | 2/3 | ||

| refresh [ms] | 64 / 16 @ 80 °C | ||

| self. ref. exit [ns] | 67 | ||

| SDTIMR | |||

| TRF_C (31-27) | 5 | 9-1 | REFR to REFR |

| T_RP (26-24) | 1 | 3-1 | PRE to ACTIV or REFR |

| (23) | 0 | 0 | |

| T_RCD (22-20) | 1 | 3-1 | ACTIV to RD/WR |

| (19) | 0 | 0 | |

| T_WR (18-16) | 1 | 2-1 | WRITE to PRE |

| T_RAS (15-12) | 80 | 6-1 | ACTIV to PRE |

| T_RC (11-8) | 5 | 9-1 | ACTIV to ACTIV |

| (7) | 0 | 0 | |

| T_RRD (6-4) | 1 | 2-1 | ACTIV to ACTIV other bank |

| (3) | 0 | 0 | |

| SDSRETR | |||

| 0 | 5+3-1 | configure refresh rate | |

| SDRCR | |||

| RR (12-0) | 2000 | 156 | 80e6 * 16e-3 / 8192 => less or equal to 156 |

| SDCR | |||

| SR (31) | 0 | 0 | self refresh mode |

| PD (30) | 0 | 0 | power down |

| PDWR (29) | 0 | 0 | refresh in PD |

| NM (14) | 1 | 1 | narrow mode |

| CL (11-9) | 3 | 3 | CAS latency |

| BIT11_9LOCK (8) | 1 | 1 | CAS latency lock |

| IBANK (6-4) | 2 | 2 (4 banks) | banks |

| PAGESIZE (2-0) | 3 | 2 (10 bit) | counted in elements |

SCI port

We have connected serial port on Expansion Connector P3 (see HDK documentation) pin W3 and N2. TX is connected to N2 pin and RX to W3 pin. This brings us consequences as both pins are mutexed.

When you want to use SCI, you have to set few things in HalCoGen.

- Enable driver SCI (not LIN or SCI2 driver)

- In tab PINMUX select SCI and check conflict with other drivers

- In tab SCI choose and set data format.

When you want use interrupts in adittion, do the following:

- In tab VIM Channel 64-95 select interrupt 64: SCI level0 interrupt for high level interrupt or 74: SCI Level1 for low level interrupt

- In SCI tab enable TX and/or RX interrupt and select High or Low.

- In your code enable IRQ using _enable_IRQ() function, than enable notification using sciEnableNotification() function.

- Implement notification callback sciNotification() in notificatin.c

In your code don't forget to initialize sci using sciInit() function.

Debug over JTAG

XDS100v2 JTAG Interface from Ti

The XDS100v2 is equipped with Ti specific 14-pin JTAG connector. Next cable wires placement allows to use it with TMS570LS31x_HDK_Kit or other device with ARM JTAG pin placement.

| 14 pin Ti | 20 pin ARM | ||

|---|---|---|---|

| 1 | TMS | TMS | 7 |

| 2 | TRST | NTRST | 3 |

| 3 | TDI | TDI | 5 |

| 4 | DIS | GND | 6 |

| 5 | VD | VREF | 1 (2) |

| 6 | NC | -- | |

| 7 | TDO | TDO | 13 |

| 8 | GND | GND | (4) |

| 9 | RTCK | RTCK | 11 |

| 10 | GND | GND | 8 (12) |

| 11 | TCK | TCK | 9 |

| 12 | GND | GND | 10 (14) |

| 13 | EMU0 | ||

| 14 | EMU1 | ||

Setup XDS100v2 on Linux

By default the device (if nothing more connected then /dev/ttyUSB0) is added with permissions 664 with

root as user and group. You access the device we need write access for current user. To do so we need

to create a new udev rules:

sudo nano /etc/udev/rules.d/45-pes-rpp.rules

And add line:

SUBSYSTEM=="usb", ATTR{idVendor}=="0403", ATTR{idProduct}=="a6d0", MODE="0660", GROUP="plugdev"

Then reload udev rules with:

sudo udevadm control --reload-rules

You can check device properties like idVendor or idProduct with the following command:

udevadm info -a -p $(udevadm info -q path -n /dev/ttyUSB0)

RS232 communication setup

Connect serial communication pins to computer's RS232 port or to USB through a FTDI adapter. If using RS232 port the

device should be /dev/ttyS0, if using FTDI it should be something like /dev/ttyUSBx

(check dmesg for details).

Make sure minicom or similar terminal program is installed:

sudo apt-get install minicom

Then configure minicon:

sudo minicom -s

And use the following configuration "9600 81N":

Serial Device : /dev/ttyS0 Lockfile Location : /var/lock Callin Program : Callout Program : Bps/Par/Bits : 9600 8N1 Hardware Flow Control : No Software Flow Control : No

Start terminal session and type HELP command to test communication.

GCC build for Cortex-R4 Big-Endian

GCC options

-mbig-endian -march=armv7-r -mthumb

GCC options with hard float

-mbig-endian -mthumb -march=armv7-r -mfpu=vfpv3-d16 -mfloat-abi=hard

GCC multilib options

armv7-r/thumb2/be;@mbig-endian@mthumb@march=armv7-r armv7-r/thumb2/vfpv3/be;@mbig-endian@mthumb@mfloat-abi=hard@march=armv7-r@mfpu=vfpv3-d16

- Patch to enable GCC and Newlib with big-endian support for RTEMS proposal

- http://lists.rtems.org/pipermail/devel/2014-June/007232.html

- Toolchain for RTEMS port to Cortex-R4F big-endian (TMS570LS3137)

- Sebastian Huber's version to push upstream

- http://lists.rtems.org/pipermail/devel/2014-July/007244.html

- RTEMS: Add multilibs for ARM

- Newlib correction

- http://lists.rtems.org/pipermail/devel/2014-July/007251.html

- Remaining arch issue in Newlib optimized ARM ASM memchr for Cortex-R

RTEMS Cortex-R4 TMS570 BSP Deveopment (GSoC 2014 project)

- http://wiki.rtems.org/wiki/index.php/RTEMSPortToCortexR4

- http://github.com/AoLaD/rtems/tree/tms570-bsp

- http://github.com/AoLaD/rtems-tms570-utils

Contacts

- Management: Prof. Zdeněk Hanzálek

- Technical: Pavel Píša, Ph.D.