FPGA simulace: Difference between revisions

No edit summary |

No edit summary |

||

| Line 123: | Line 123: | ||

[[Image:dinotrace.png|frame|Simulovane prubehy zobrazene v Dinotrace]] | [[Image:dinotrace.png|frame|Simulovane prubehy zobrazene v Dinotrace]] | ||

[[Category: | [[Category:FPGA]] | ||

Latest revision as of 17:40, 7 November 2010

Zkouseny a zkusebni VHDL kod

Chceme simulovat odezvu vlastnich bloku, napsanych ve VHDL. Prikladem budiz ctyrbitovy citac File:Citac.vhdl:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity citac is

port (

clock: in std_logic;

qcount: out std_logic_vector (3 downto 0)

);

end citac;

architecture behavioral of citac is

signal counter: std_logic_vector (3 downto 0) := "0000";

begin

qcount <= counter;

seq: process

begin

wait until clock'event and clock = '1';

counter <= counter + 1;

end process;

end behavioral;

Je treba vyplnit u registru pocatecni podminky (signal counter: std_logic_vector (3 downto 0) := "0000";). Uvedeny citac ma vyvedeny signaly clock (vstup hodin) a qcount (4bit vystup). Nyni je treba vytvorit (opet ve VHDL) zkusebni nastroj (testbench), do nehoz bude citac (a pripadne i vice bloku) zapojen a ktery bude generovat zkusebni vstupni signaly. V tomto pripade je zkusebni signal jednoduchy, staci periodicke hodiny na signal clock.

Zde je kod zkusebniho nastroje File:Citac tb.vhdl:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity citac_tb is

end citac_tb;

architecture behavioral of citac_tb is

component citac

port (

clock: in std_logic;

qcount: out std_logic_vector (3 downto 0)

);

end component;

for citac_0: citac use entity work.citac;

--

signal clock: std_logic;

signal qcount: std_logic_vector (3 downto 0);

begin

citac_0: citac

port map (

clock => clock,

qcount => qcount

);

--

process

begin

clock <= '0';

wait for 1 us;

clock <= '1';

wait for 1 us;

end process;

end behavioral;

Entita nahore je prazdna, protoze zkusebni nastroj nema ven vyvedeny zadne signaly, neni to potreba. Nize je pak instanciovan citac a v tele nastroje je nekonecne dlouho bezici proces, ktery periodicky strida urovne na signalu clock. Je samozrejme mozne utvorit i konecne dlouho bezici zkusebni nastroje. Cas 1us jsem zvolil libovolne.

Simulace v GHDL

VHDL soubory je nyni mozne zkompilovat simulatorem GHDL

ghdl -a --ieee=synopsys citac.vhdl ghdl -a --ieee=synopsys citac_tb.vhdl

a slinkovat do spustitelneho souboru:

ghdl -e --ieee=synopsys citac_tb

Volba --ieee=synopsys je pouzita proto, ze jsem v prikladu pouzil nestandardni datove typy, obvykle ve svete FPGA, ale nestandardni vzhledem k IEEE VHDL. (Nerikam, ze je to dobre, chce to zjistit, zda se standardem budeme schopni vystacit.)

Nasledne spustime simulaci

ghdl -r citac_tb --vcd=citac.vcd

...ta bezi nekonecne, takze ji prerusime Ctrl-c. Byl zadan vystup do souboru ve formatu VCD, kde by se mely objevit prubehy vsech signalu.

Prohlizeni prubehu

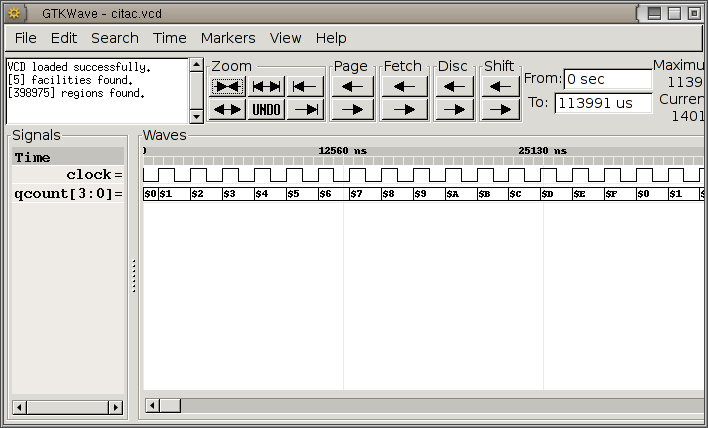

GtkWave

Soubor citac.vcd prohledneme pomoci GtkWave:

gtkwave citac.vcd

Pokud nas udivi, ze vidime jen casovou osu a zadne signaly, je treba v menu Search / Signal search hierarchy.. pridat signaly, ktere nas zajimaji, tedy clock a qcount.

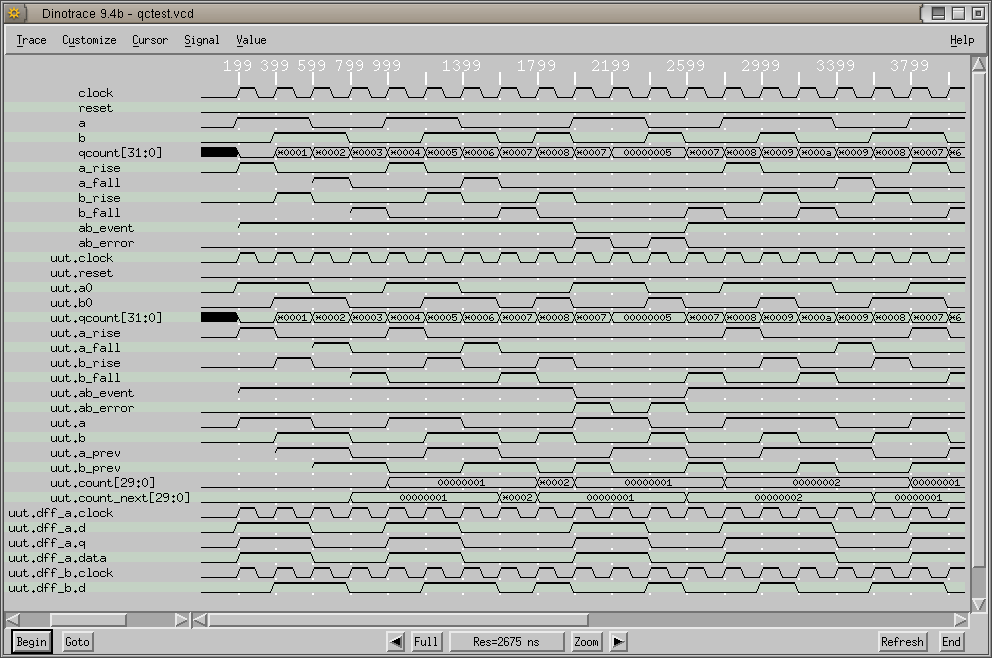

Dinotrace

Nekomu muze vice vyhovovat program Dinotrace. Mj. nacita rovnez format .vcd. Priklad zobrazeni signalu z mirne slozitejsiho obvodu je zde: