Academy of Sciences of the Czech Republic Institute of Information Theory and Automation

# Outline

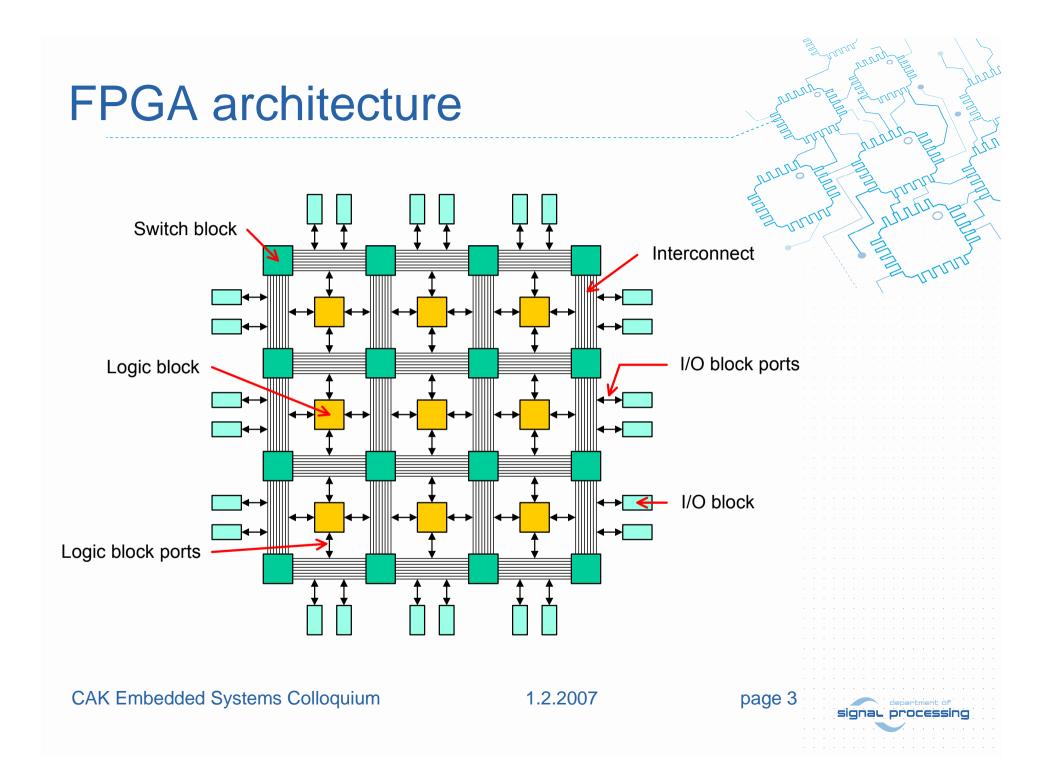

FPGA architecture Iogic blocks, interconnect resources Partial dynamic reconfiguration Static and dynamic part, bus macros Constraints Demonstrator Reconfigurable FIR filter MicroBlaze, System ACE, DDR, ICAP Implementation - Xilinx ML402 platform

CAK Embedded Systems Colloquium

1.2.2007

page 2

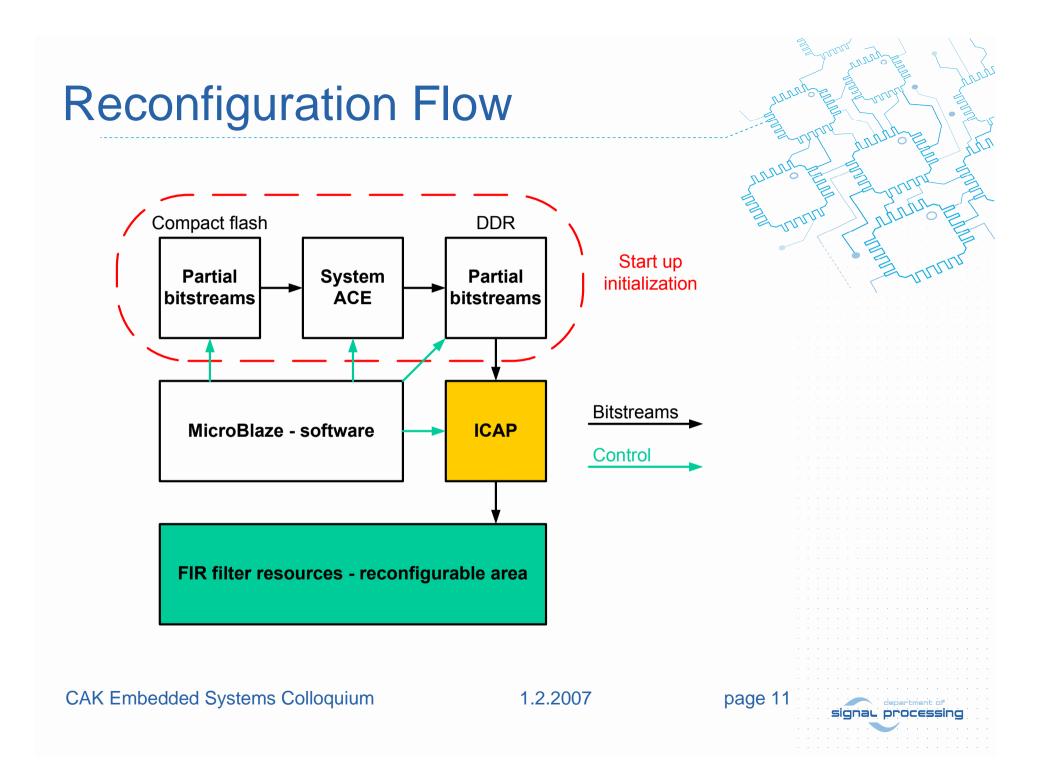

#### Partial Dynamic Reconfiguration

▷ Virtex<sup>TM</sup>-II, Virtex-II Pro, and Virtex-4

- Multiple design modules to time-share physical resources

- Dynamic modules can be swapped on the fly

- Modular design required

- Dynamic modules with identical interface

page 4

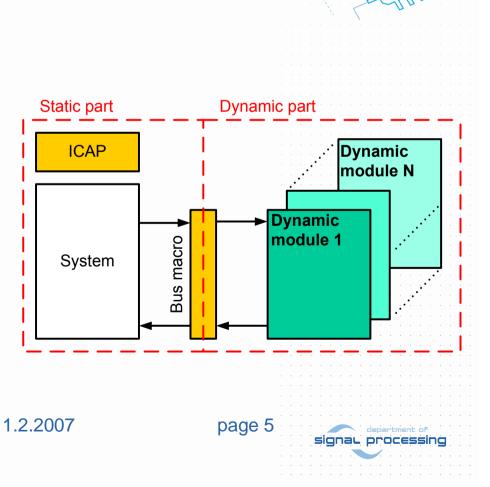

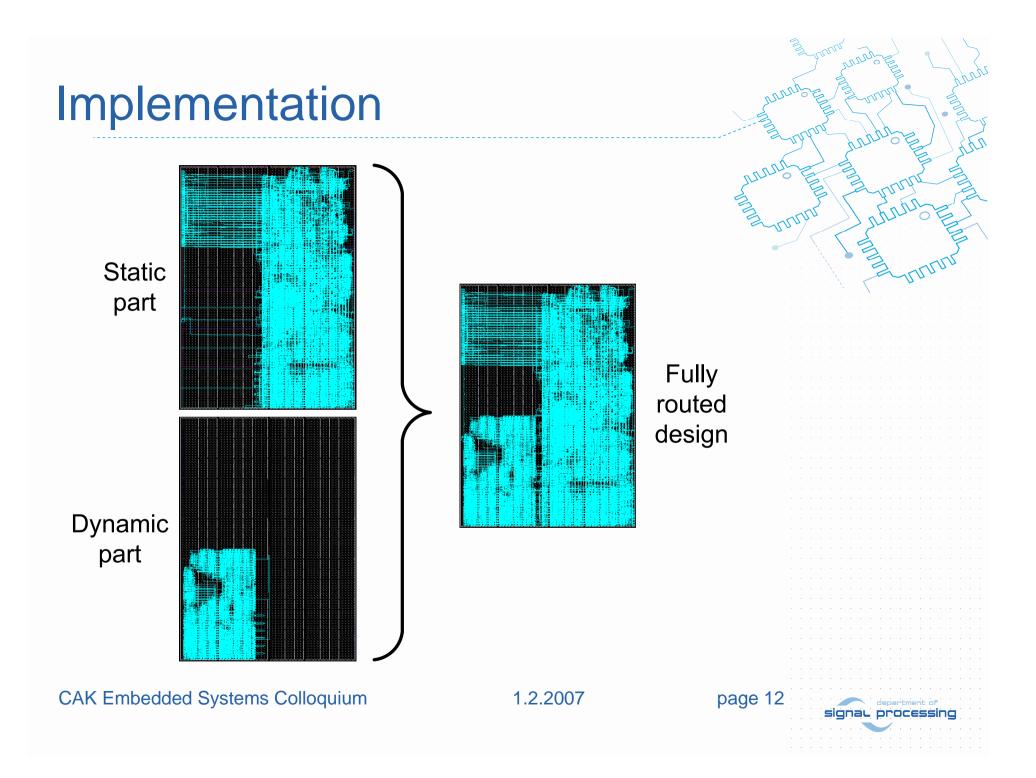

## **Static and Dynamic Part**

- The static part is running all the time.

- The dynamic part is reconfigured on the fly.

- The interface between the static and dynamic part is formed by a bus macro.

#### **Bus Macro**

- Means of locking the routing between the dynamic and the static part

- All connections between the dynamic and static part must pass through a bus macro

- The clock signal is an exception

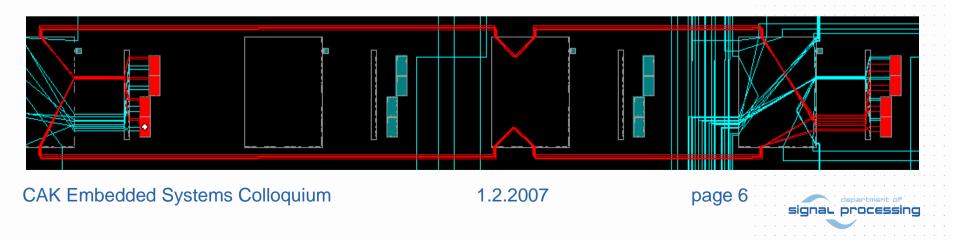

#### Constraints

Knowledge of the placement

- Static part

- Dynamic part can include more independent reconfigurable areas

- Bus macros

- Specified in the \*.ucf file

#### Demonstrator

#### FIR filter

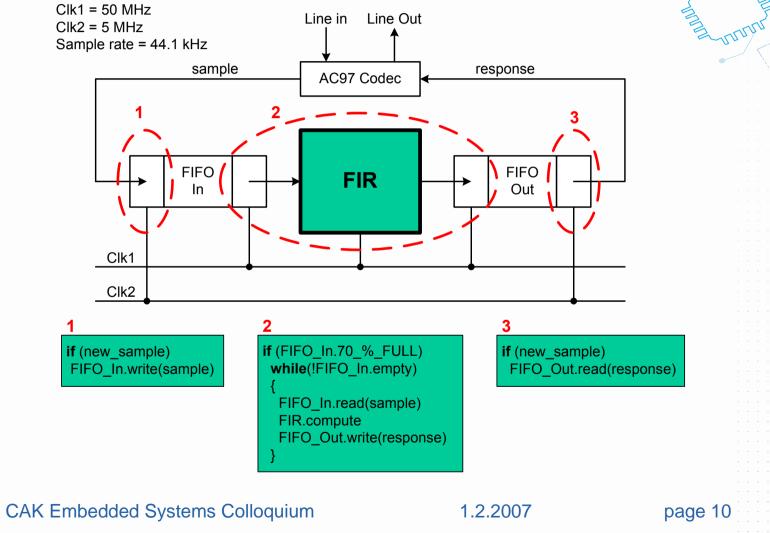

- I6 bit sample/response (audio data)

- 15 weights

- ▷ Low pass filter ( $f_c = 4 \text{ kHz}$ )

- High pass filter (f<sub>c</sub> = 4 kHz)

- Sample rate = 44.1 kHz

- Xilinx ML402 evaluation platform

MicroBlaze

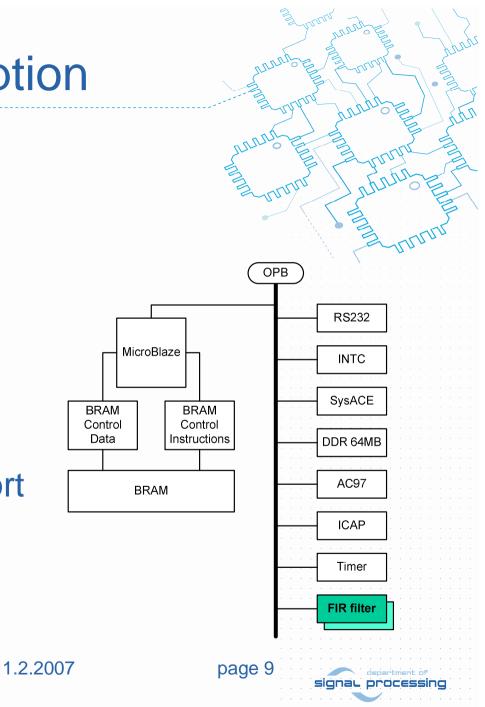

### **Demonstrator Description**

- Static part

- MicroBlaze

- System ACE

- DDR 64 MB

- AC97 codec

- ICAP Internal Configuration Access Port

- Dynamic partFIR filter

CAK Embedded Systems Colloquium

#### **Data Flow**

department of

## Implementation (2)

#### Used resources in Virtex-4 SX35

|                                        | Static | FIR HP | FIR LP | Total<br>(fully static) | Total PR<br>impl. | PR impl. vs.<br>fully static |

|----------------------------------------|--------|--------|--------|-------------------------|-------------------|------------------------------|

| Number of Slice Flip Flops             | 4719   | 549    | 608    | 5876                    | 5327              | 9 %                          |

| Number of 4 input LUTs                 | 4359   | 3651   | 3480   | 11490                   | 8010              | 30 %                         |

| Number of occupied Slices              | 4513   | 2318   | 2270   | 9149                    | 6831              | 25 %                         |

| Total Number 4 input LUTs              | 5121   | 3831   | 3702   | 12654                   | 8952              | 29 %                         |

| Number used as logic                   | 4359   | 3651   | 3480   | 11490                   | 8010              | 30 %                         |

| Number used as a route-thru            | 23     | 181    | 222    | 426                     | 245               | 42 %                         |

| Number used for Dual Port RAMs         | 568    | 0      | 0      | 568                     | 568               | 0 %                          |

| Number used as Shift registers         | 171    | 0      | 0      | 171                     | 171               | 0 %                          |

| Number used as FIFO16s                 | 0      | 0      | 0      | 0                       | 0                 | 0 %                          |

| Number used as RAMB16s                 | 33     | 0      | 0      | 33                      | 33                | 0 %                          |

| Number of DSP48s                       | 3      | 0      | 0      | 3                       | 3                 | 0 %                          |

| Number of hard macros                  | 6      | 0      | 0      | 0                       | 6                 | -100 %                       |

| Number of ICAP_VIRTEX4s                | 1      | 0      | 0      | 0                       | 1                 | -100 %                       |

| Total equivalent gate count for design | 119334 | 47024  | 43840  | 210198                  | 166358            | 20 %                         |

CAK Embedded Systems Colloquium

1.2.2007

signa

## Implementation (3)

Design clock = 50 MHz

Reconfiguration latency

344 ms - 211 kB

346 ms - 212 kB

1.2.2007

## Conclusions

- The use of partial dynamic reconfiguration for effective implementation of the FIR filters

- The internal ICAP reconfiguration interface reduces the reconfiguration time significantly.

- Our experiments show the saved FPGA resources.

## Acknowledgements

- This work has been partially supported by:

- the Czech Ministry of Education Project No. 1M0567 http://www.c-a-k.cz

- the European Commission Project No. FP6-2004-IST-4-027611 http://www.aether-ist.org