# USING RECONFIGURABLE HW FOR HIGH DIMENSIONAL CAF COMPUTATION

#### Antonín Heřmánek, Michal Kuneš

Institute of Information Theory and Automation Academy of Sciences of the Czech Republic, Prague, Czech Republic email: {hermaneke, xkunes}@utia.cas.cz

March 27, 2006

## **OUTLINE**

## MOTIVATION Cross Ambiguity function

System Settings

#### Algorithms for FFT

#### System Architecture

Architecture of the L0 stage Architecture of the L1 stage Architecture of the L2 stage Overall architecture Time Scheduling

#### IMPLEMENTATION AND RESULTS

- Modern radar system use Passive Coherent Location (PCL)

- Systems with no emitation only "listen"

- PCL exploit high-power commercial transmitters (FM, TV, etc.)

- evaluates a function related to direct and reflected signals from localized targets

- The function to be evaluate = Cross Ambiguity function (CAF)

## CROSS AMBIGUITY FUNCTION

CAF represents the power spectral density distribution of the cross-correlation between direct and reflected signals:

$$A(\tau,k) = \sum_{n=0}^{N-1} s_1(n) s_2^*(n+\tau) e^{-j2\pi kn/N}$$

(1)

$s_1, s_2$  discrete-time analytic (complex) signals

N is the integration period

au is time delay

k Doppler frequency offset

The magnitude of  $A(\tau, k)$  peaks when  $\tau$  and k/N are equal to the TDOA and/or FDOA between signals  $s_1$  and  $s_2$ .

## Cross Ambiguity function – cont.

The effective CAF computation use direct application of the FFT into signal product of the signals  $s_1$  and  $s_2$ .

$$A(\tau,k) = FFT(s_1(n)s_2^*(n+\tau))$$

(2)

To calculate CAF using this formula for all values of  $\tau$  and k, an individual FFT computation is required for each value of  $\tau$ .

The basic requirements on CAF calculation engine for PCL system signal processing are as follows:

- Sampling frequency: 100-200 kHz

- Effective bit resolution of input signals: 18-24 bits

- Integration interval:  $N = 2^{17} = 131\,072$  samples

- ullet Frequency resolution:  $< 1~{

m Hz}$

- Accuracy of the CAF calculation: absolute error about 10<sup>-10</sup> compared to the IEEE 64-bit floating-point arithmetic

- Maximum number of time delays: < 600</li>

- Maximum frequency range:  $\langle -300: +300 \rangle Hz$  ( 601 spectral coefficients)

- Total time of computation: < 1 sec</li>

## ALGORITHMS FOR FFT

#### KNOWN ALGORITHMS

- FFT (radix -2, radix-4, split radix)

- Zoom-FFT

- Pre-weighted FFT

- Goertzel algorithm

#### SUITABLE ALGORITHMS FOR PCL

- FFT (any radix) only!

- other methods inserts a systematic error and/or are more complex for a given interval of frequency bins

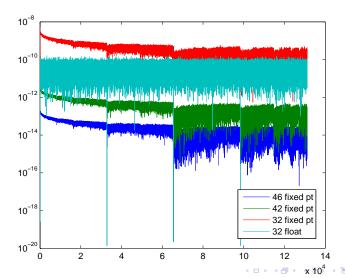

## NUMERICAL REQIREMENTS

#### Conclusion

- we need at least 42 bits in fixed point

- 32-bit IEEE floating point is on the boundary

#### AVAILABLE FFT ON FPGA

- non of the commercial nor open source such long and such accurete FFT IP core

- Xilinx: FFT length  $2^{16} = 65\,536$  at 24 bits (fixed pt. or block floating pt.)

- Altera:  $2^{14}c = 16384$  at 24 bits fixed point

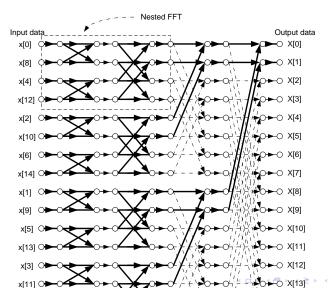

## FFT WITH REDUCED NUMBER OF OPERATION

## System Architecture

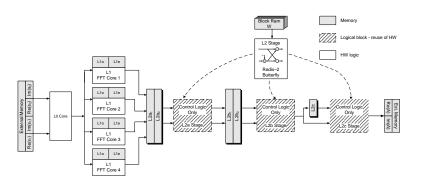

#### STRUCTURE OF LONG FFT CALC

STAGE L0: signal multiplication  $s_1(n)s_2^*(n+\tau)$

STAGE L1: parallel calculation of nested FFTs of size  $N_f$

STAGE L2: calculation of the rest of butterflies

#### TIMING

- stage L1 represents  $N/N_f=128$  nested FFTs using mono processor approach, takes 589,824 cycles.

- stage L2, takes approximately 76, 928 cycles.

- it follows that the most computationally intensive part is the computation of stage L1.

## BLOCK STRUCTURE OF LO STAGE

- All data paths and operation are complexnumbers/paths.

- to shorten the calculation L1 stage, the first radix-2 butterfly (addition/subtraction only) is calculated in stage L0

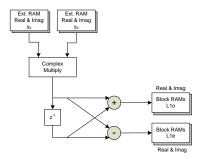

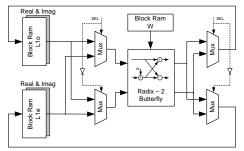

## BLOCK STRUCTURE OF THE L1 STAGE

- Since the calculation of the nested FFTs is the most computationally intensive operation, four L1 cores are used in parallel

- Using two dual ported memories, two input and two output values are read/stored at the same time – the Radix-2 core is fully utilized.

- L2 architecture is the same as L1

- it uses a set of tables W of size Δ each.

- To optimize the size of intermediate memory and time schedule, the L2 block is divided to tree logic parts:

- L2A, L2B implements three stages of FFT i.e. from  $2^3\Delta$  inputs and calculates  $\Delta$  intermediate values

- L2C L2c implements the final one stage i.e. from  $2\Delta$  values calculates final  $\Delta$  results. It use one table W

- all three parts L2a, L2b and L2c use the same hardware core only one part can run at a time

## BLOCK ARCHITECUTURE OF THE SYSTEM

## TIME SCHEDULING

## TIME SCHEDULING - CONT.

| Stage                | Clock              | Comp.          | Comp.          |

|----------------------|--------------------|----------------|----------------|

| _                    | Cycles             | 33MHz          | 66MHz          |

| data load L1         | 1034               | $31.3 \mu s$   | $15,7\mu s$    |

| data store L1        | 304                | $9.21 \mu s$   | $4.61 \mu s$   |

| data load L2a,b      | 624                | $18.9 \mu s$   | $9.4 \mu s$    |

| data store L2a,b     | 606                | $18.3 \mu s$   | $9.1 \mu s$    |

| data load L2c        | 609                | $18.4 \mu s$   | $9.2 \mu s$    |

| data store L2c       | 609                | $18.4 \mu s$   | $9.2 \mu s$    |

| computation L1       | 4805               | $146 \mu s$    | $72.8 \mu s$   |

| computation L2a, L2b | 4263               | $129 \mu s$    | 64.6 <i>µs</i> |

| computation L2c      | 608                | $18.4 \mu s$   | $9.21 \mu s$   |

| computation 1xFFT    | $219 \cdot 10^{3}$ | 6,64 <i>ms</i> | 3,32 <i>ms</i> |

| computation CAF      | $131 \cdot 10^6$   | 3, 98 <i>s</i> | 1,99 <i>s</i>  |

IMPLEMENTATION AND RESULTS

| Utilization of XC4VSX55 |       |      |  |  |

|-------------------------|-------|------|--|--|

| DSP48s                  | 216   | 42%  |  |  |

| RAMB16s                 | 170   | 53 % |  |  |

| LUTs                    | 25394 | 51 % |  |  |

| Slices                  | 16482 | 67 % |  |  |

| Flip Flops              | 19266 | 39 % |  |  |

| Utilization of EP2S180 |       |      |  |  |

|------------------------|-------|------|--|--|

| DSP9s                  | 624   | 81 % |  |  |

| M512s                  | 846   | 90 % |  |  |

| M4Ks                   | 472   | 61 % |  |  |

| M-RAMs                 | 4     | 44 % |  |  |

| ALUTs                  | 48924 | 34 % |  |  |

| ALMs                   | 27180 | 37 % |  |  |

| Registers              | 25729 | 17 % |  |  |

О

## **END**